- Heat flow is changed inside the chip components instead of being removed after accumulation

- The movement of phonons is limited by the structuring of the surface at the nanoscale

- Ultrafast lasers enable nanoscale modeling at industrially relevant speeds

Today, most electronic devices rely on heat sinks, fans, or liquid cooling because components inside chips conduct heat in a fixed manner.

A new method designed by Japanese researchers allows engineers to control how quickly heat escapes from a material, rather than simply trying to release heat once it has built up.

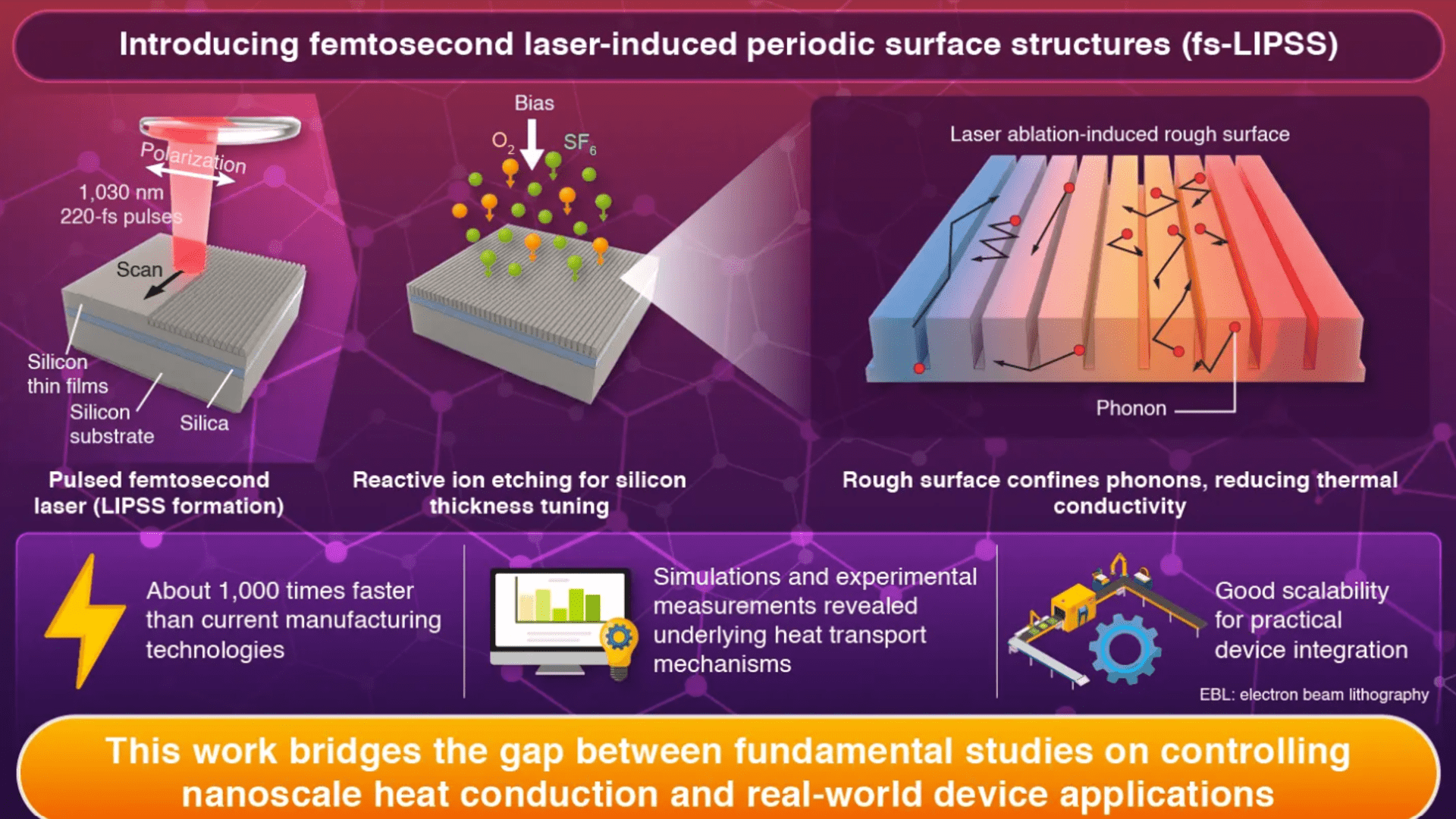

The work describes a laser-based manufacturing method that changes the way heat moves through thin films of silicon and silica by directly shaping their surfaces at the nanoscale.

Modification of heat transport at the chip component level

The approach relies on ultrafast laser pulses, each lasting one femtosecond, to ablate material and create parallel grooves on the film surface.

These grooves form with carefully controlled spacing and depth that closely match the average distance phonons travel before scattering.

Since phonons are the primary heat carriers in these components, restricting their movement predictably changes the overall thermal conductivity.

The resulting features, known as femtosecond laser-induced periodic surface structures, exhibit high uniformity over relatively large areas.

When combined with conventional dry etching to adjust film thickness, patterned surfaces exhibit a marked reduction in thermal conductivity.

Thermoreflectance measurements quantified this change, providing experimental confirmation rather than inferred behavior.

Numerical simulations also showed that the reduction results mainly from limited phonon travel distances rather than changes in the chemical composition or properties of the bulk materials.

A central claim of the study concerns manufacturing speed. The fs-LIPSS process would operate at a throughput more than 1,000 times faster than single-beam e-beam lithography, while achieving nanoscale resolution.

This difference is substantial, especially for applications requiring large structured areas, such as thermal layers embedded in data center processors.

The process is maskless and resistor-free, reducing procedural complexity and aligning with standard CMOS manufacturing constraints.

The technique has also been described as capable of being implemented at wafer scale without introducing additional components or lithographic steps.

Since the method avoids resistors and masks, it remains compatible with established semiconductor workflows.

The researchers describe the process as scalable, semiconductor-ready, and suitable for integration with existing manufacturing lines.

The nanostructures are described as mechanically robust, with reports indicating strength levels up to 1,000 times greater than those produced using some conventional patterning approaches.

However, the available description provides limited details on direct mechanical comparative analysis or comparative testing methods.

The technique appears promising and is relevant to high-performance computing, quantum devices, and thermal management challenges associated with dense GPU clusters powering modern AI tools.

But wider adoption will depend on reproducibility, long-term stability and cost under industrial conditions, particularly at data center deployment scale.

Via Tokyo Institute of Science

Follow TechRadar on Google News And add us as your favorite source to get our news, reviews and expert opinions in your feeds. Make sure to click the Follow button!

And of course you can too follow TechRadar on TikTok for news, reviews, unboxings in video form and receive regular updates from us on WhatsApp Also.